# A Low-IF RX Two-Point $\Sigma\Delta$ -Modulation TX CMOS Single-Chip Bluetooth Solution

Christian Dürdodt, Martin Friedrich, *Member, IEEE*, Christian Grewing, Markus Hammes, *Member, IEEE*, André Hanke, *Member, IEEE*, Stefan Heinen, Jürgen Oehm, Duyen Pham-Stäbner, Dietolf Seippel, Detlev Theil, Stefan van Waasen, and Elmar Wagner, *Member, IEEE*

**Abstract**—A new low-cost concept for a system-on-chip Bluetooth solution is proposed in this paper. The single chip includes all necessary baseband and RF parts to achieve full Bluetooth functionality and is implemented in a standard 0.25- $\mu\text{m}$  CMOS technology. The two-point modulation  $\Sigma\Delta$  fractional  $N$  phase-locked loop achieves a phase noise of  $-124$  dBc/Hz at 3-MHz offset. The sensitivity of the embedded low-IF receiver is measured to be  $-82$  dBm at a bit error rate of 0.1%. The power supply voltages for the digital and analog parts are internally regulated to 2.65 V. The maximum current consumption of the analog part is 60 mA.

**Index Terms**—Communication systems, CMOS analog integrated circuits, CMOS digital integrated circuits, RF radio communication, RF receivers, RF transmitters, sigma-delta modulation, wireless LAN.

## I. INTRODUCTION

THE new short-range communication standard Bluetooth<sup>1</sup> wireless technologies enables the *ad hoc* networking of devices like mobile phones, laptops, palmtops, etc. in the unlicensed 2.4-GHz industrial–scientific–medical (ISM) band. Low cost, low power consumption, and small feature size are the main design issues for Bluetooth interfaces.

The used modern CMOS technology allows the integration of the baseband and RF parts on the same die, which minimizes cost and size. A careful floor planning, layout arrangements, isolation concept, system architecture, and circuit design are combined to achieve an optimum isolation between these parts and, thus, an optimized performance. Two completely independent and separately located voltage regulators minimize the digital crosstalk via the power supplies to the analog RF parts. A coil is implemented only for the voltage-controlled oscillator (VCO), whereas for the low-noise amplifier (LNA), an inductorless architecture is chosen. This prevents inductive

crosstalk among transmit and receive path and reduces size. Closed-loop modulation and the earliest reasonable change into the digital domain in the receiver (RX) result in a robust crosstalk insensitive system solution. The single chip is highly integrated ( $>10^6$  transistors) and realizes all system functions needed for communication under the Bluetooth standard. The single-chip system incorporates the transceiver for the 2.4-GHz ISM frequency band, with an on-chip output driver, a fully differential LNA, and a channel select filter. Together with the Bluetooth software “Pro-Blue,” which includes the host controller interface (HCI) and link manager (LM), a system for Bluetooth wireless technology can be developed. To compose the complete hardware for a Bluetooth interface, only a few external (passive) components are needed. Thus, the main design issues for Bluetooth interfaces are attained with the proposed CMOS system on-chip Bluetooth solution.

## II. ARCHITECTURE

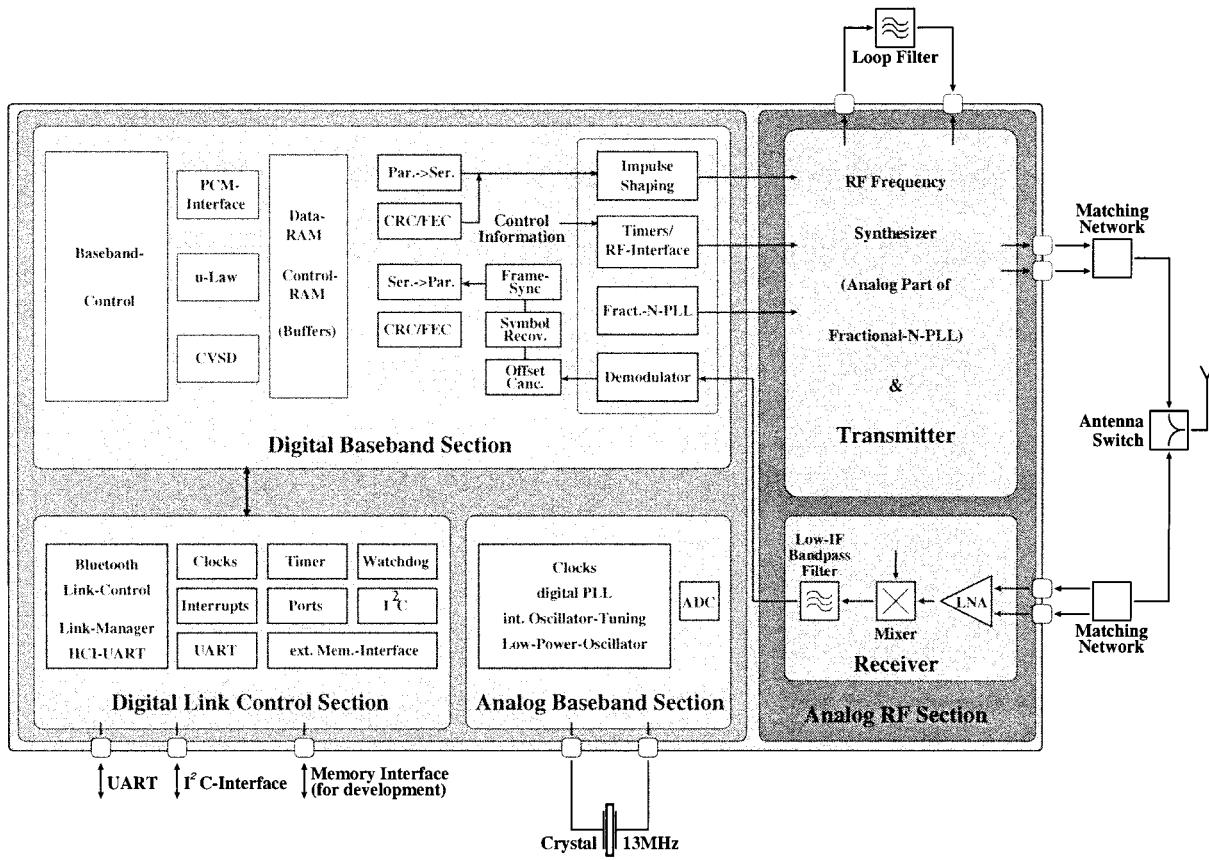

The proposed low-cost single-chip architecture is depicted in Fig. 1. The baseband and RF parts will be discussed in detail below.

### A. Baseband Part

The baseband part can be divided into the digital baseband section, the analog baseband section, and the link control section.

Within the digital baseband section, the demodulation unit is located, as well as the digital part of the  $\Sigma\Delta$  fractional  $N$  phase-locked loop (PLL), and the control logic for the analog RF section, including timing, power, and Gaussian frequency shift keying (GFSK) modulation control for the PLL. An amplitude tunable Gaussian impulse forming filter is implemented to achieve the matching between the two modulation paths of the  $\Sigma\Delta$  fractional  $N$  PLL.

In the analog baseband section, an 8-bit A/D converter for the radio signal strength indicator (RSSI) information from the RX is placed, as well as the 13-MHz crystal oscillator, its associated clock generation, and the voltage regulator for the digital power supply.

The link control section includes the link control management unit, and several I/O interfaces for application flexibility (e.g., four-wire pulse-code modulation (PCM) interface, universal asynchronous receiver transmitter (UART), I<sup>2</sup>C interface, memory interface). During startup, the digital control reads the configuration information from the external E<sup>2</sup>PROM, like

Manuscript received March 30, 2001.

C. Dürdodt is with the Microelectronics Development Center, Infineon Technologies AG, D-40489 Düsseldorf, Germany in cooperation with the Electrical Engineering Department, Ruhr-Universität Bochum, D-44780 Bochum, Germany.

M. Friedrich, C. Grewing, M. Hammes, A. Hanke, S. Heinen, J. Oehm, D. Pham-Stäbner, D. Seippel, S. van Waasen, and E. Wagner are with the Microelectronics Development Center, Infineon Technologies AG, D-40489 Düsseldorf, Germany.

D. Theil is with the Microelectronics Development Center, Infineon Technologies AG, D-40489 Düsseldorf, Germany and is also with the Department of Microelectronics, University of Dortmund, D-44227 Dortmund, Germany.

Publisher Item Identifier S 0018-9480(01)07576-7.

<sup>1</sup>Bluetooth is a trademark owned by its proprietor and used by Infineon Technologies AG under license.

Fig. 1. Bluetooth SOC block diagram.

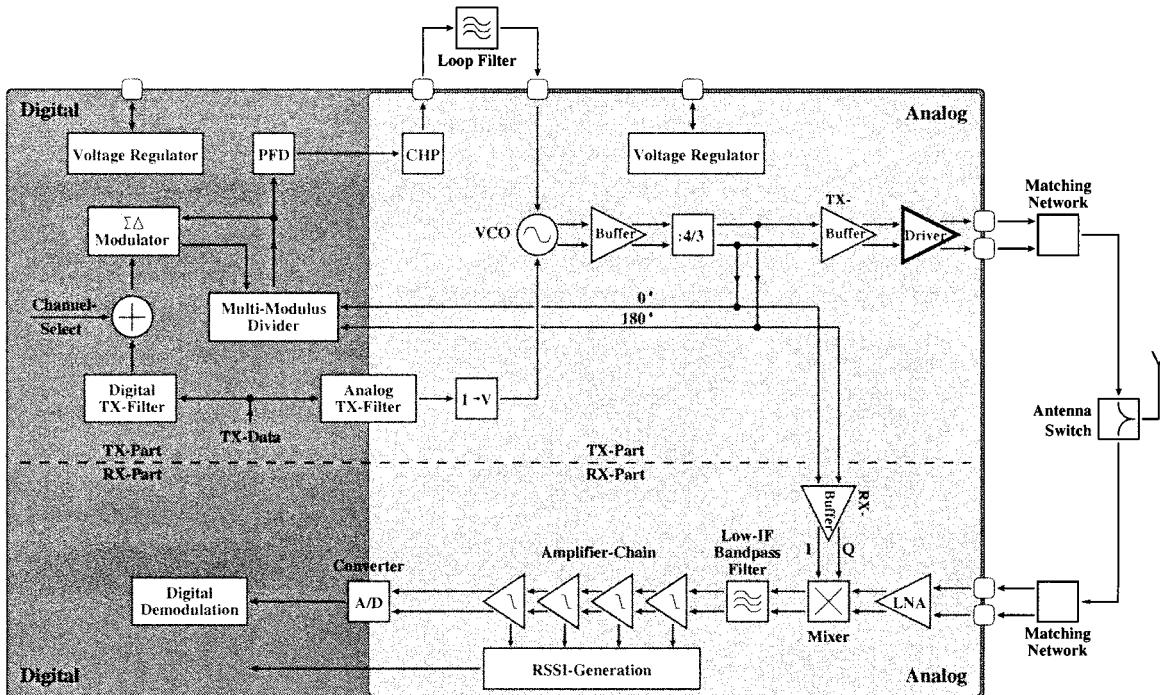

Fig. 2. Block diagram of the RF part.

crystal adjustment, the Bluetooth device address, etc. All other functions are done via host controller interface universal asynchronous receiver transmitter (HCI UART). Therefore, no hardware-specific firmware or software development has to be done.

### B. RF Part

The RF section is depicted in more detail in Fig. 2. It can be divided into the transmitter (TX) and RX parts.

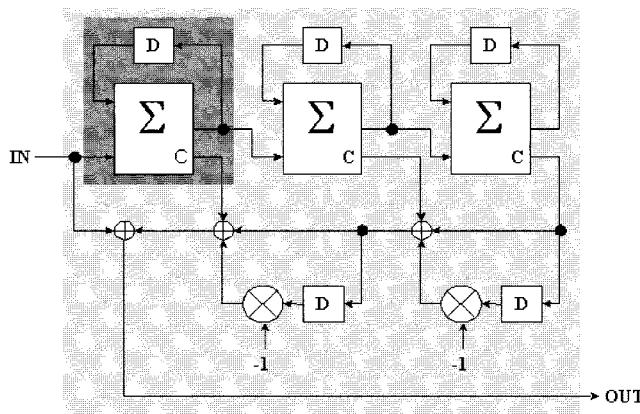

Fig. 3. Structure of the cascaded 1-1-1 MASH  $\Sigma\Delta$  modulator.

1) *TX Architecture*: The part is based on the Bluetooth TX described in [2]. In the TX part, a  $\Sigma\Delta$  fractional  $N$  PLL is realized. It contains a phase frequency detector (PFD), a chargepump (CHP), a multimodulus divider (MMD), a fully integrated VCO with a VCO buffer and 4/3 frequency converter, as well as a TX buffer and TX driver. The loop filter is realized as an external passive third-order filter. The maximum output power of the TXA driver is measured to be 0 dBm. The 13-MHz on-chip crystal oscillator provides the digital clock frequency and the reference for the phase-frequency detector.

Due to the feedback dynamics of the PLL, the maximum data rate is limited. To overcome the limited PLL bandwidth in order to achieve the 1-Mbit/s two-GFSK modulation, a two-point closed-loop modulation scheme is used. The gauss filtered data are injected into the loop at two different points via a low- and high-pass modulation path.

For the low-pass modulation, the digitally Gaussian shaped TX data are added to the channel word at the input of the  $\Sigma\Delta$  modulator and, therefore, injected into the loop via the fully programmable MMD. Depending on the value of the parallel 7-bit output data stream of the  $\Sigma\Delta$  modulator, the MMD divides the input frequency by a value of

$$N_{\text{div}} = 128 + \sum_{n=0}^6 b_n \cdot 2^n.$$

The structure of the cascaded multistage noise shaping (MASH)  $\Sigma\Delta$  modulator is shown in Fig. 3. Its noise-shaping characteristic [3] allows the shift of low-frequency noise to higher frequencies, where it is attenuated by the loop filter.

The high-pass modulation is injected into the loop by direct VCO modulation. The incoming Gaussian shaped TX-impulse sequences are D/A converted within the analog section. The D/A conversion is done with weighted current sources. The output current is I/V converted and low-pass filtered next and given to the modulation input of the VCO.

The summation of both modulation paths allows to overcome the limited bandwidth of the PLL and, therefore, to modulate the VCO with frequencies beyond the loop bandwidth.

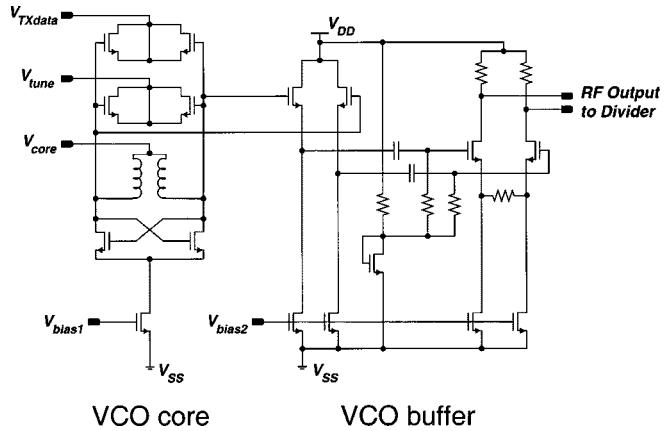

The fully integrated VCO is shown in Fig. 4. It contains a negative-transconductance ( $G_m$ )  $LC$  resonator with a cross-coupled pair of NMOS transistors as the active part. The  $LC$  resonator is implemented as an on-chip spiral inductor and NMOS varac-

Fig. 4. Schematic of the 3.2-GHz VCO with additional modulation input.

tors. These varactors are realized by using the depletion region of the capacitance characteristic of the transistors. By making use of these separate voltage-dependent capacitors within the VCO circuitry, the VCO frequency and, therewith, the transmit frequency, is finally Gaussian modulated—separately from the VCO tuning.

The VCO operates at 4/3 of the nominal TX frequency to avoid VCO pulling due to the output driver. The conversion to 2.4 GHz is achieved with an up-conversion image-reject mixer.

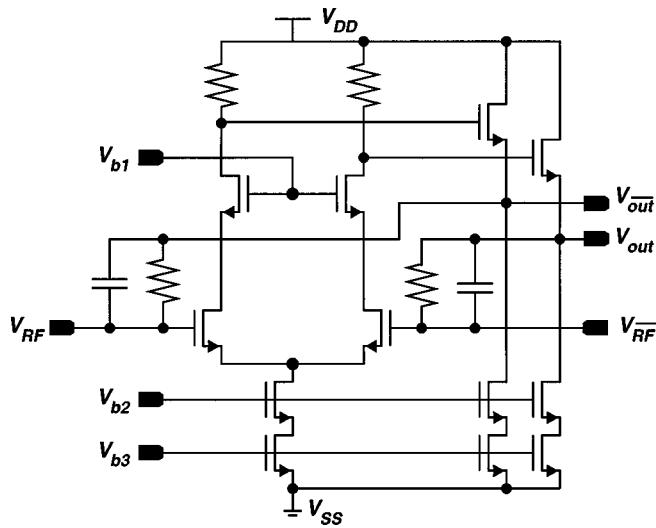

2) *RX Architecture*: The advantages of a “classical IF” RX and a zero-IF RX are combined in the chosen low-IF RX architecture [4]. Due to the possible integration of the channel-select filter, the integration level is equivalent with a zero-IF architecture, without the drawback of the well known dc-offset problem. Furthermore, the passive external high- $Q$  filter for image rejection—needed in high-IF RXs—is replaced by a untuned, broadband, and, therefore, cheap filter. The IF of 1 MHz allows an ac coupling between the amplifier stages to remove static and dynamic offsets without affecting the desired signal. The RX is implemented fully differential to reduce the influence of switching noise from the digital circuits. Due to the low-crosstalk sensitivity, the LNA (Fig. 5) is implemented as an inductorless cascaded differential amplifier. A mixture of resistive and capacitive feedback is used to achieve a resistive input impedance. An external balun (matching network) is needed for the single-ended to differential conversion of the antenna signal.

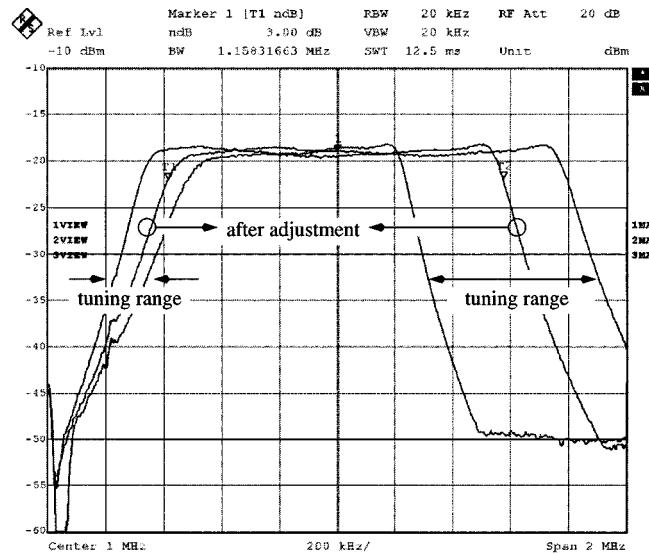

The RF signal is down converted to the IF of 1 MHz by an in/quadrature phase (I/Q) mixer. A passive polyphase filter performs the  $0^\circ$  and  $90^\circ$  phase shift of the local oscillator (LO) signal for the receive mixer [5]. A fifth-order automatic adjusted polyphase filter is implemented for channel-select filtering in the complex domain. The complex signal processing allows the attenuation of the image without effecting the wanted signal at 1 MHz. As is well known from homodyne RXs and image reject mixers, a mismatch between the signal paths leads to a reduced image rejection [6]. The image frequency attenuation is directly correlated with the matching in the polyphase filter and LO mixers. The relative matching error between the resistors is kept smaller than 1%. The passband of the single-sideband bandpass is about 1 MHz, centered at 1 MHz. One-fourth of the filter area is occupied by switchable capacitors to tune out tolerances. The cutoff frequency can be adapted during the automatic

Fig. 5. Schematic of the inductorless LNA.

adjustment before every receive time slot in the range of  $\pm 20\%$ . Two folded cascode operational amplifiers with a dc gain of 60 dB form a discrete pole of the filter. Each op-amp consumes 1.75 mW and contains an independent common-mode feedback loop. Overall, the filter has a linear input range of 600 mV, which is sufficient due to the output compression voltage of the front end. The noise figure of the filter is 22 dB. Due to the balanced design of the I/Q mixer, LO path, and polyphase filter, an overall RX image rejection of  $>28$  dB is provided, which is sufficient for Bluetooth. The signals are amplified by a chain of ac-coupled amplifiers. The total gain of the amplifier chain is  $>80$  dB. The analog representation of the RSSI signal is generated from the outputs of the first amplifiers and A/D converted for further digital processing. The dynamic range of the RSSI signal is  $>55$  dB. A self-calibrating biasing is used in each amplifier stage to reduce static and dynamic offsets. The differential signal at the end of the amplifier chain is A/D converted and demodulated in the digital part.

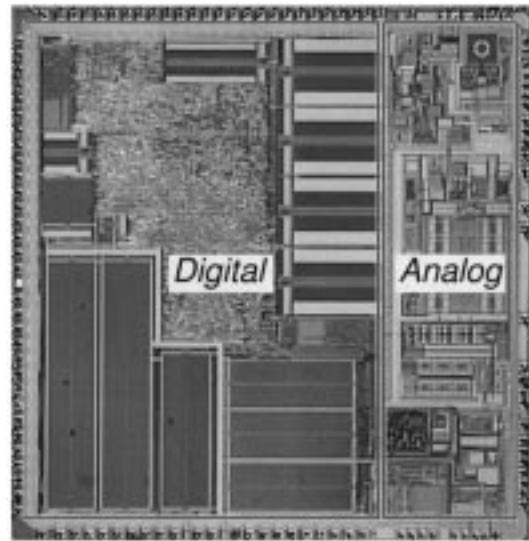

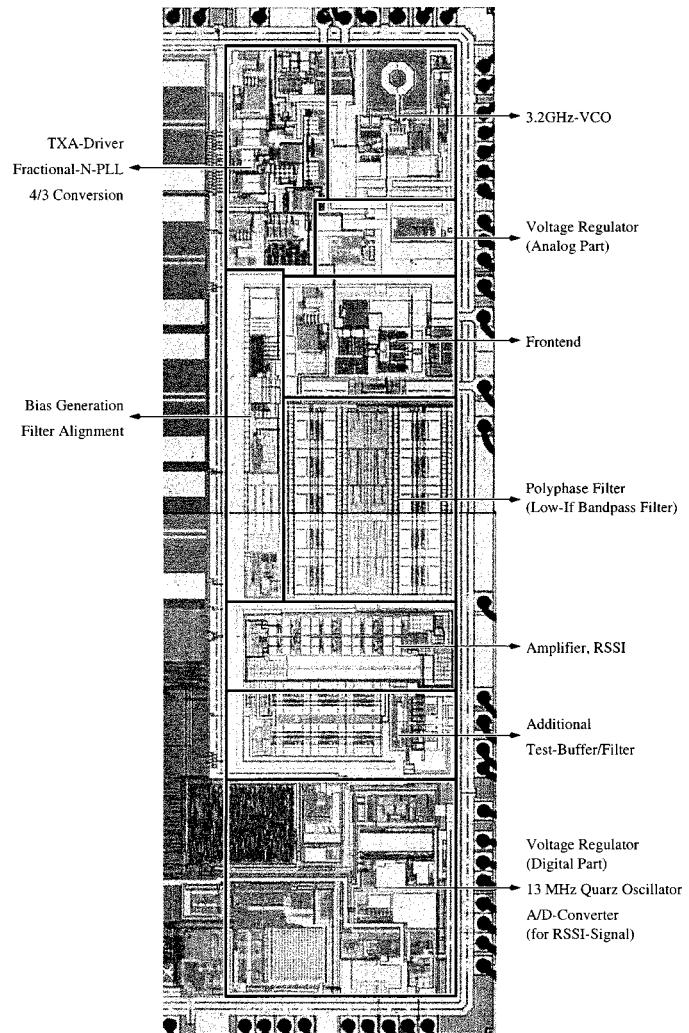

Fig. 6 shows a chip photograph of the entire single chip. The baseband part covers roughly 3/4 and the RF part covers 1/4 of the occupied area. A careful floor planning and the use of guard rings and shieldings provide the optimum isolation between the analog and digital parts. In Fig. 7, the chip photograph of the RF part is shown. To give an idea of the required area of the introduced analog functional blocks, their placement is marked.

### III. MEASUREMENTS

Initial measurement results indicate good function of all implemented analog and digital blocks. Successful bidirectional data transfers between the Bluetooth single chip and other listed Bluetooth transceivers over a distance of  $>14$  m point out the functioning of the proposed concept.

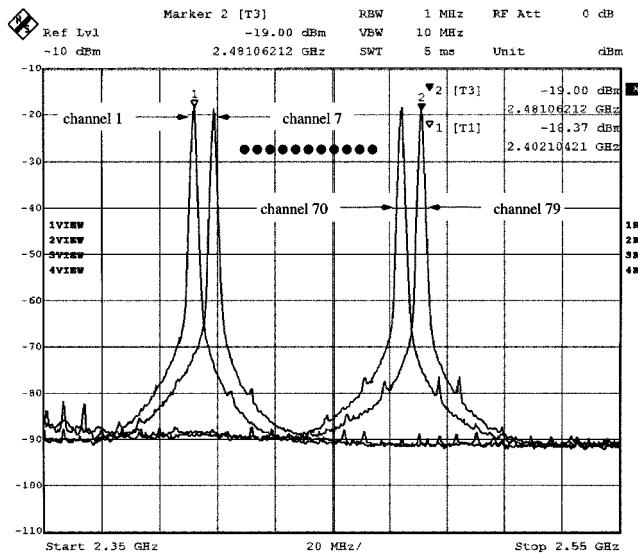

The VCO provides a tuning sensitivity of about 635 MHz/V, by consuming 4 mA from the 2.65-V supply. The tuning range spans from 3.1 to 3.4 GHz. As shown in Fig. 8, the digitally controlled fractional  $N$  PLL locks at the 79 Bluetooth channels by

Fig. 6. Die photograph of the single chip.

Fig. 7. Die photograph of the RF part.

achieving a channel independent phase noise of  $-124$  dBc/Hz at 3-MHz offset.

Fig. 8. Output spectrum of the PLL at different Bluetooth channels.

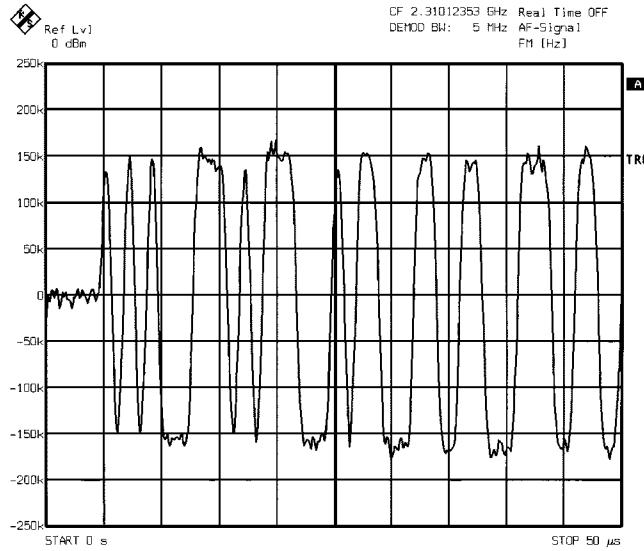

Fig. 9. Demodulated transmitted Gauss impulse sequence.

The Gaussian shape of the demodulated transmitted signal, shown in Fig. 9, indicates the wanted interaction of the two PLL modulation paths. The TXA driver provides an output power of 0 dBm. For higher power levels, an optional external power amplifier (PA) can be used.

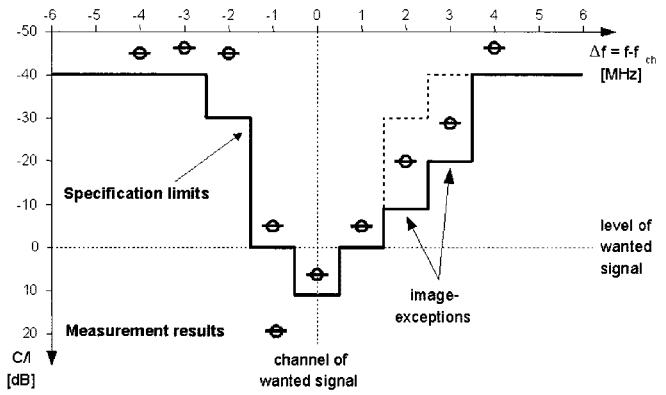

The minimum detectable RX signal is  $-82$  dBm at 0.1% BER, which is 12 dB better than required. The measured in-band blocker rejection is shown in Fig. 10. The minimum margin to the Bluetooth RX interference specification is 4 dB for the co-channel, which is set by the demodulator capture range. The adjacent channel rejection is set by the rolloff of the channel-select filter. The image rejection is 28–29 dB, which is nearly 10 dB better than required for the Bluetooth standard. In Fig. 11, the measured ac response of the fifth-order polyphase filter can be seen. After passing the automatic adjustment cycles, the ac response of the filter meets exactly the wanted characteristics. Furthermore, the available tuning range of the filter corner frequencies indicates that fabrication tolerances can easily be balanced.

Fig. 10. RX interference performance at 0.1% BER.

Fig. 11. AC response of the fifth-order polyphase filter.

The maximum current consumption of the analog part is 60 mA. The benefit of an inductorless RX is the low-crosstalk sensitivity and the small size, which simplifies a Bluetooth single-chip solution. The supply voltage of the digital and analog parts is 2.65 V, and both are internally regulated.

#### IV. CONCLUSION

A low-cost concept for a CMOS system on chip Bluetooth solution has been presented in this paper. The measurement results meet the Bluetooth specifications<sup>2</sup> and show the suitability of the presented single-chip concept.

The crosstalk between the analog and digital parts is the drawback of single-chip solutions. This effect is kept small by the proposed crosstalk-insensitive system concept, circuit design, and layout. In a further redesign, the current consumption of the baseband and RF parts will be reduced and the RX sensitivity increased. Due to the need of only a few external elements and a reasonable power consumption, the proposed single-chip solution fulfills the main design issues for small-size low-cost Blue-

<sup>2</sup>Bluetooth Version 1.0B, 1999. [Online]. Available: <http://www.bluetooth.com>

tooth interfaces. Within the next redesign step, full Bluetooth performance and reduced power consumption will be achieved.

#### ACKNOWLEDGMENT

The authors would like to thank M. Diedrichs, Microelectronics Development Center, Infineon Technologies, Düsseldorf, Germany, for excellent layout support.

#### REFERENCES

- [1] J. P. K. Gilb, "Bluetooth radio architectures," in *IEEE RFIC Symp. Dig.*, June 2000, pp. 3–6.

- [2] D. Theil, C. Dürdodt, A. Hanke, S. Heinen, S. vanWaasen, D. Seippel, D. Pham-Stäbner, and K. Schumacher, "A fully integrated CMOS frequency synthesizer for Bluetooth," in *IEEE RFIC Symp. Dig.*, May 2001, pp. 103–106.

- [3] S. R. Norsworthy, R. Schreier, and G. C. Temes, *Delta-Sigma Data Converters: Theory, Design, and Simulation*. Piscataway, NJ: IEEE Press, 1997.

- [4] J. Crols and M. Steyaert, "A single-chip 900 MHz CMOS receiver front-end with a high performance low-IF topology," *IEEE J. Solid-State Circuits*, vol. 30, pp. 1483–1492, Dec. 1995.

- [5] J. Janssens, M. Steyaert, B. De Muer, M. Borremans, and N. Itoh, "A 2 V CMOS cellular transceiver front-end," in *IEEE Int. SSC Conf.*, 2000, pp. 142–143.

- [6] A. A. Abidi, "Direct-conversion radio transceivers for digital communications," *IEEE J. Solid-State Circuits*, vol. 30, pp. 1399–1409, Dec. 1995.

Germany.

**Christian Dürdodt** received the Dipl.-Ing. degree in electrical engineering from the Ruhr-Universität Bochum, Bochum, Germany, in 1998. Since 1998, he has been with the Microelectronics Development Center, Infineon Technologies, Düsseldorf, Germany, where he is working toward the Dr.-Ing. degree in electrical engineering in cooperation with the Ruhr-Universität Bochum, Bochum, Germany.

Since 1998, he has been with the Microelectronics Development Center, Infineon Technologies AG (formerly Siemens Semiconductors), Düsseldorf, Germany.

**Martin Friedrich** (S'94–M'97) received the Dipl.-Ing. degree in electrical engineering from the Ruhr-Universität Bochum, Bochum, Germany, in 1992, and the Ph.D. degree from the Institute of Microelectronics (Arbeitsgruppe Halbleiterbauelemente), Ruhr-Universität Bochum, in 2000.

From 1992 to 2000, he was a Research Assistant at the Institute of Microelectronics. Since 2000, he has been with the Microelectronics Development Center, Infineon Technologies AG (formerly Siemens Semiconductors), Düsseldorf, Germany.

**Christian Grewing** received the Dipl.-Ing. degree from the Ruhr-Universität Bochum, Bochum, Germany, in cooperation with the Microelectronics Development Center, Siemens Semiconductors, Düsseldorf, Germany, in 1998.

Since 1998, he has been with Siemens Semiconductors (now Infineon Technologies AG), Düsseldorf, Germany, where he is engaged in the field of short-range wireless systems, where he is currently involved with transceivers, with special focus on system-on-chip (SOC).

systems.

**Markus Hammes** (M'93) received the Dipl.-Ing. degree from the University Duisburg, Duisburg, Germany, in 1992 and the Ph.D. degree from the Rheinisch-Westfälische Technische Hochschule (RWTH)-Aachen Institute of Technology, Aachen, Germany, in 1998.

Since 1998, he has been with Infineon Technologies AG (formerly Siemens Semiconductors), Düsseldorf, Germany, where he is involved in the area of wireless communications and is responsible for system and concept engineering for cordless

**André Hanke** (M'98) received the Dipl.-Ing. degree from the University of Bochum, Bochum, Germany, in 1995.

From 1993 to 1995, he was with Siemens Semiconductors. In 1995, he joined Philips Semiconductors. Since 1997, he has been with Infineon Technologies AG (formerly Siemens Semiconductors), Düsseldorf, Germany, where he was engaged in different RF projects. He is currently responsible for a design group dealing with RF innovation projects.

digital enhanced cordless telecommunications (DECT).

**Stefan Heinen** received the Dipl.-Ing. and Ph.D. degrees from Duisburg University, Duisburg, Germany, in 1988 and 1992, respectively.

Since 1992, he has been with Infineon Technologies AG (formerly Siemens Semiconductors), Düsseldorf, Germany, where he has been involved in different positions in the research and development (R&D) of commercial integrated solutions for wireless communications. He currently heads the RF R&D Group, in which he is involved with short-range wireless systems like Bluetooth and

circuits and statistic simulations. He also holds a post-doctoral university lecturing qualification.

**Jürgen Oehm** received the Engineer and Doctor-Engineer degrees from the University of Dortmund, Dortmund, Germany, in 1987 and 1992, respectively.

Since 1987, he has been involved with the measurement and modeling of statistical mismatch effects between monolithic integrated structures and the computational simulation of those effects on analog circuits and systems. In 1999, he joined Infineon Technologies AG (formerly Siemens Semiconductors), Düsseldorf, Germany, where he has been involved with the design of analog RF

circuits and statistic simulations. He also holds a post-doctoral university lecturing qualification.

**Duyen Pham-Stäbner** received the Dipl.-Ing. degree in electrical engineering from the University of Dortmund, Dortmund, Germany, in 1999.

Since 1999, she has been with Infineon Technologies AG (formerly Siemens Semiconductors), Düsseldorf, Germany, where she is a member of the Innovation Group of RF Chip Design, Microelectronics Development Center.

**Dietolf Seippel** received the Dipl.-Ing. degree in electrical engineering from the Ruhr-Universität Bochum, Bochum, Germany, in 1994.

From 1994 to 1999, he was with the Smart Power Group, SICAN, Hannover, Germany. Since 1999, he has been with the Microelectronics Development Center, Infineon Technologies AG (formerly Siemens Semiconductors), Düsseldorf, Germany, where he is currently involved with RFCMOS transceiver design for wireless communications integrated circuits (ICs).

**Stefan van Waasen** received the Dipl.-Ing. degree and the Ph.D. degree in electrical engineering from Duisburg University, Duisburg, Germany, in 1994 and 1999, respectively.

Since 1998, he has been with Infineon Technologies AG (formerly Siemens Semiconductors), Düsseldorf, Germany, where he is involved in the field of wireless communications. His responsibilities are in the area of system and concept engineering with special focus on SOC.

**Detlev Theil** received the M.S. degree in electrical engineering from the University of Dortmund, Dortmund, Germany, in 1998, and is currently working toward the Ph.D. degree at the University of Dortmund.

He is currently with the Microelectronics Development Center, Infineon Technologies AG (formerly Siemens Semiconductors), Düsseldorf, Germany.

**Elmar Wagner** (M'99) received the Dipl.-Ing. degree from the University of Bochum, Bochum, Germany, in 1988.

In 1991, he joined Philips, where he was involved in the development of DECT telephones. In 1994, he joined Philips Semiconductors. In 1999, he joined Infineon Technologies AG (formerly Siemens Semiconductors), Düsseldorf, Germany, where he is currently responsible for the Concept Engineering Group for short-range wireless RF ICs such as Bluetooth and DECT.